# MF610 Single-Phase BLDC Motor Controller Data Sheet

Version 0.05 - Aug. 17, 2023

Copyright  ${\scriptsize ©}$  2023 by PADAUK Technology Co., Ltd., all rights reserved.

6F-6, No.1, Sec. 3, Gongdao 5th Rd., Hsinchu City 30069, Taiwan, R.O.C. TEL: 886-3-572-8688 🙀 www.padauk.com.tw

# **IMPORTANT NOTICE**

PADAUK Technology reserves the right to make changes to its products or to terminate production of its products at any time without notice. Customers are strongly recommended to contact PADAUK Technology for the latest information and verify whether the information is correct and complete before placing orders.

PADAUK Technology products are not warranted to be suitable for use in life-support applications or other critical applications. PADAUK Technology assumes no liability for such applications. Critical applications include, but are not limited to, those that may involve potential risks of death, personal injury, fire or severe property damage.

Any programming software provided by PADAUK Technology to customers is of a service and reference nature and does not have any responsibility for software vulnerabilities. PADAUK Technology assumes no responsibility for any issue caused by a customer's product design. Customers should design and verify their products within the ranges guaranteed by PADAUK Technology. In order to minimize the risks in customers' products, customers should design a product with adequate operating safeguards.

#### Table of Contents

| 1. | . Key Features                                                                     | 5  |

|----|------------------------------------------------------------------------------------|----|

| 2. | Pin Diagram and Pin Description                                                    | 6  |

| 3. | Device Characteristics                                                             | 7  |

|    | <ul><li>3.1. Absolute Maximum Ratings</li><li>3.2. DC/AC Characteristics</li></ul> |    |

| 4. | . Reference Application Circuit                                                    | 10 |

| 5. | . Package Information: MSOP10 (118mil)                                             | 11 |

#### **Revision History:**

| Revision | Date       | Description                                                                                                      |

|----------|------------|------------------------------------------------------------------------------------------------------------------|

| 0.04     | 2021/01/15 | Add pin description                                                                                              |

|          |            | 1. Updated "IMPORTANT NOTICE"                                                                                    |

| 0.05     | 2023/08/17 | 2. Updated DC/AC Characteristics: $f_{SYS}$ , $I_{OP}$ , $V_{BRD}$ , $V_{BG}$ , $f_{IHRC}$ , $V_{ADC}$ and ADclk |

|          |            | 3. Amend chapter 4 (three-phase diagram)                                                                         |

#### 1. Key Features

- Single-phase BLDC motor with hall IC interface

- PWM or voltage control input

- FG/RD/ALM/RALN/RXX/RRXX output

- Close loop or/and open loop control

- Current limit and over-current protection

- Soft-start, lock-protect and auto-restart

- System protection

- Low-voltage detection with reset

- Illegal opcode detection with reset

- MTP Programming

- Support 6-wire factory programming mode

- Support 4-wire in-system programming mode

- DC Fan Applications

- Operating voltage range: 3.5V~6V

- Operating temperature range: -40°C~105°C

- Package Information

- MF610-M10: MSOP10 (118mil)

MF610 is a single phase BLDC motor controller based on 8-bit 8-FPPA MCU which can be programmed by 6-wire factory mode or 4-wire ISP mode. MF610 receives motor position signal from Hall IC and can control the H-bridge flexibly to make the best efficiency of the motor. Through the PADAUK patented AP development system, it can easily set any speed curve, output signal and protection parameters etc., and it can observe the motor response online immediately. Using the MF610's development system, it's much easier and adjustable for application.

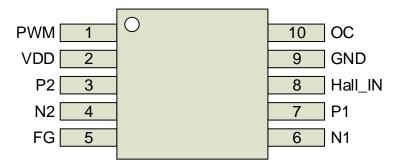

### 2. Pin Diagram and Pin Description

MF610: M10 (MSOP10-118mil)

| Pin Name           | I/O                                                          | Description                                               |  |  |  |  |  |

|--------------------|--------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|

| PWM/ PB7           | Input                                                        | PWM signal input                                          |  |  |  |  |  |

| VDD                | -                                                            | Power pin. Needs a 1uF and a 0.1uF capacitor in parallel. |  |  |  |  |  |

| P2/ PA6            | Output                                                       | Output signal to control the high side of motor driver    |  |  |  |  |  |

| N2/ PA7            | Output Output signal to control the low side of motor driver |                                                           |  |  |  |  |  |

| FG/ PA0            | Output                                                       | Rotation speed signal output                              |  |  |  |  |  |

| N1/ PA3            | Output                                                       | Output signal to control the low side of motor driver     |  |  |  |  |  |

| P1/ PA4 Output     |                                                              | Output signal to control the high side of motor driver    |  |  |  |  |  |

| Hall_IN/ PA5 Input |                                                              | Digital hall signal input                                 |  |  |  |  |  |

| GND                | -                                                            | Ground                                                    |  |  |  |  |  |

| OC/ PB0            | Input                                                        | Analog input to sense motor current                       |  |  |  |  |  |

#### 3. Device Characteristics

#### 3.1. Absolute Maximum Ratings

| Name                  | Min  | Тур. | Мах                   | Unit | Notes                                                   |

|-----------------------|------|------|-----------------------|------|---------------------------------------------------------|

| Supply Voltage (VDD)  | 3.5  |      | 6                     | V    | Exceed the maximum rating may cause permanent damaged!! |

| Input Voltage         | -0.3 |      | V <sub>DD</sub> + 0.2 | V    |                                                         |

| Operating Temperature | -40  |      | 105                   | °C   |                                                         |

| Storage Temperature   | -50  |      | 125                   | °C   |                                                         |

| Junction Temperature  |      | 150  |                       | °C   |                                                         |

#### 3.2. DC/AC Characteristics

| Symbol           | Description                                                 | Min                 | Тур       | Max                | Unit | Conditions (Ta=25℃)                                               |

|------------------|-------------------------------------------------------------|---------------------|-----------|--------------------|------|-------------------------------------------------------------------|

| V <sub>DD</sub>  | Operating Voltage                                           | 3.5                 | 5.0       | 6                  | V    | -40 °C <ta<85 td="" °c<=""></ta<85>                               |

| VDD              |                                                             | 4.75                | 5.0       | 6                  | •    | -40 °C <ta<105 td="" °c<=""></ta<105>                             |

| VFSV             | Forbidden V <sub>DD</sub> startup voltage range             | 0.7                 |           | 1.6                | V    |                                                                   |

| VPORV            | V <sub>DD</sub> power down release voltage                  |                     |           | 0.7                | V    |                                                                   |

| T <sub>POR</sub> | $V_{\text{DD}}$ power on time (V_{\text{DD}} from 0V to 5V) |                     |           | 50                 | ms   |                                                                   |

| T <sub>FSV</sub> | V <sub>DD</sub> power on time during V <sub>FSV</sub> range |                     |           | 10                 | ms   |                                                                   |

| fsys             | System clock<br>IHRC/2                                      | 0                   |           | 8M                 | Hz   | V <sub>DD</sub> = 3.3V                                            |

| I <sub>OP</sub>  | Operating Current                                           |                     | 3.5       |                    | mA   | f <sub>SYS</sub> =8MIPS@5.0V                                      |

| 1                | Power Down Current                                          |                     | 3         |                    | uA   | V <sub>DD</sub> =5.0V                                             |

| I <sub>PD</sub>  | (by <i>stopsys</i> command)                                 |                     | 1         |                    | uA   | V <sub>DD</sub> =3.3V                                             |

| IPS              | Power Save Current<br>(by <b>stopexe</b> command)           |                     | 0.4       |                    | mA   | VDD=5.0V;<br>Bandgap, LVD, IHRC, ILRC,<br>Timer16 modules are ON. |

| VIL              | Input low voltage for IO lines                              | 0                   |           | 0.2V <sub>DD</sub> | V    |                                                                   |

| Vін              | Input high voltage for IO lines                             | 0.8 V <sub>DD</sub> |           | Vdd                | V    |                                                                   |

| I <sub>OL</sub>  | IO lines sink current                                       | 11                  | 14        | 17                 | mA   | $V_{DD}$ =5.0V, $V_{OL}$ =0.5V                                    |

| Іон              | IO lines drive current                                      | -8                  | -10       | -12                | mA   | V <sub>DD</sub> =5.0V, V <sub>OH</sub> =4.5V                      |

| R <sub>PH</sub>  | Pull-high Resistance                                        |                     | 90<br>170 |                    | KΩ   | V <sub>DD</sub> =5.0V<br>V <sub>DD</sub> =3.3V                    |

| Vbrd             | Low Voltage Detect Voltage *<br>(Brown-out voltage)         | 3.0                 | 3.3       | 3.5                | V    |                                                                   |

©Copyright 2023, PADAUK Technology Co. Ltd

| Symbol           | Description                                                                                      | Min    | Тур    | Max    | Unit   | Conditions (Ta=25℃)                                                    |

|------------------|--------------------------------------------------------------------------------------------------|--------|--------|--------|--------|------------------------------------------------------------------------|

| M                | Bandgap Reference Voltage (before calibration)                                                   | 1.12   | 1.20   | 1.28   | v      | V <sub>DD</sub> =5V, 25°C                                              |

| V <sub>BG</sub>  | Bandgap Reference Voltage *<br>(after calibration)                                               | 1.17*  | 1.20*  | 1.23*  | V      | V <sub>DD</sub> =3.3V ~ 5.5V,<br>-40°C <ta<105°c*< td=""></ta<105°c*<> |

|                  |                                                                                                  | 15.52* | 16*    | 16.48* | MHz    | 25°C, V <sub>DD</sub> =3.3V~5.5V                                       |

| fihrc            | Frequency of IHRC after<br>calibration *                                                         | 14*    | 16*    | 17.28* |        | V <sub>DD</sub> =3V~5.5V,<br>-40ºC <ta<105ºc*< td=""></ta<105ºc*<>     |

|                  |                                                                                                  | 31.5*  | 33.8*  | 35*    |        | V <sub>DD</sub> =5.0V, Ta=25°C                                         |

|                  |                                                                                                  | 29*    | 33.8*  | 38.4*  |        | V <sub>DD</sub> =5.0V, -40°C <ta<85°c*< td=""></ta<85°c*<>             |

| filrc            | Frequency of ILRC *                                                                              | 32*    | 34*    | 35.5*  | KHz    | V <sub>DD</sub> =3.3V, Ta=25°C                                         |

|                  |                                                                                                  | 29*    | 34*    | 40*    |        | V <sub>DD</sub> =3.3V, -40°C <ta<85°c*< td=""></ta<85°c*<>             |

| V <sub>ADC</sub> | Workable ADC operating<br>Voltage                                                                | 3.3    |        | 6.0    | V      |                                                                        |

| Vad              | AD Input Voltage                                                                                 | 0      |        | Vdd    | V      |                                                                        |

| ADrs             | ADC resolution                                                                                   |        |        | 11     | bit    |                                                                        |

| ADclk            | ADC clock period                                                                                 |        | 2      |        | us     | 3.3V ~ 5.5V                                                            |

| tadconv          | ADC conversion time<br>(T <sub>ADCLK</sub> is the period of the<br>selected AD conversion clock) |        | 14     |        | TADCLK |                                                                        |

| AD DNL           | ADC Differential NonLinearity                                                                    |        | ±3*    |        | LSB    |                                                                        |

| AD INL           | ADC Integral NonLinearity                                                                        |        | ±3*    |        | LSB    |                                                                        |

| ADos             | ADC offset*                                                                                      |        | 3<br>4 |        | LSB    | -40°C <ta<85°c*<br>-40°C <ta<105°c*< td=""></ta<105°c*<></ta<85°c*<br> |

| t <sub>INT</sub> | Interrupt pulse width                                                                            | 30     |        |        | ns     | $V_{DD} = 5.0 V$                                                       |

| Vdr              | RAM data retention voltage*                                                                      | 1.5    |        |        | V      | In power-down mode.                                                    |

| twpt             | Watchdog timeout period                                                                          |        | 4096   |        |        | misc[1:0]=01                                                           |

|                  | (T <sub>ILRC</sub> is the clock period of ILRC)                                                  |        | 16384  |        |        | misc[1:0]=10                                                           |

| t <sub>SBP</sub> | System boot-up period from power-on                                                              |        | 1024   |        | TILRC  | Where T <sub>ILRC</sub> is the clock<br>period of ILRC                 |

| Symbol | Description                      | Min | Тур                  | Max                  | Unit  | Conditions (Ta=25℃)                  |

|--------|----------------------------------|-----|----------------------|----------------------|-------|--------------------------------------|

|        | System wake-up period            |     |                      |                      |       |                                      |

|        | Fast wake-up by IO toggle from   |     | 128                  |                      | Tsys  | Where T <sub>SYS</sub> is the time   |

|        | STOPEXE suspend                  | 120 |                      |                      | 1313  | period of system clock               |

|        | Fast wake-up by IO toggle from   |     | 128 Tsys             |                      |       | Where $T_{SIHRC}$ is the stable time |

|        | STOPSYS suspend, IHRC is         |     | +                    |                      |       | of IHRC from power-on.               |

| twue   | the system clock                 |     | T <sub>SIHRC</sub>   |                      |       |                                      |

| WUP    | Fast wake-up by IO toggle from   |     | $128 T_{\text{SYS}}$ |                      |       | Where $T_{SILRC}$ is the stable time |

|        | STOPSYS suspend, ILRC is         |     | +                    |                      |       | of ILRC from power-on.               |

|        | the system clock                 |     | TSILRC               |                      |       |                                      |

|        | Normal wake-up from              |     |                      |                      |       | Where TILRC is the clock             |

|        | STOPEXE or STOPSYS               |     | 1024                 |                      | TILRC | period of ILRC                       |

|        | suspend                          |     |                      |                      |       |                                      |

| HCPos  | Comparator offset*               | -   | ±10                  | ±20                  | mV    |                                      |

| HCPcm  | Comparator input common<br>mode* | 0   |                      | V <sub>DD</sub> -1.5 | V     |                                      |

| HCPspt | Comparator response time**       |     | 100                  | 500                  | ns    | Both Rising and Falling              |

| HCPmc  | Stable time to change            |     | 2.5                  | 7.5                  | us    |                                      |

|        | comparator mode                  |     | 2.0                  | 7.0                  | uo    |                                      |

\*These parameters are for design reference, not tested for every chip.

\*\* Response time is measured with comparator input at (V<sub>DD</sub>-1.5)/2 -100mV, and (V<sub>DD</sub>-1.5)/2+100mV

The characteristic diagrams are the actual measured values. Considering the influence of production drift and other factors, the data in the table are within the safety range of the actual measured values.

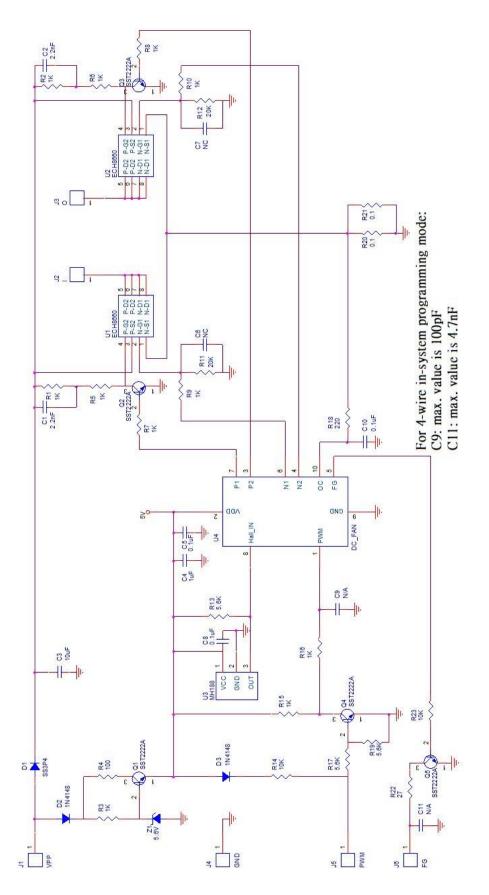

#### 4. <u>Reference Application Circuit</u>

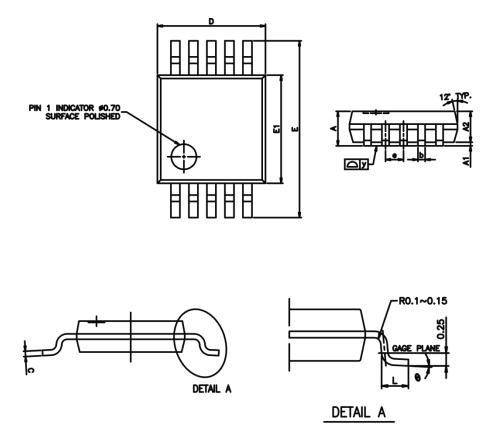

#### 5. Package Information: MSOP10 (118mil)

|         | DIMENSIONS IN MILLIMETERS |      |       |  |  |  |  |

|---------|---------------------------|------|-------|--|--|--|--|

| SYMBOLS | MIN                       | NOM  | MAX   |  |  |  |  |

| A       | -                         | -    | 1.10  |  |  |  |  |

| A1      | 0.05                      |      | 0.15  |  |  |  |  |

| A2      | 0.75                      | 0.86 | 0.95  |  |  |  |  |

| b       | 0.17                      | 0.20 | 0.27  |  |  |  |  |

| C       | 0.08                      | 0.15 | 0.23  |  |  |  |  |

| D       | 2.90                      | 3.00 | 3.10  |  |  |  |  |

| Ε       | 4.80                      | 4.90 | 5.00  |  |  |  |  |

| E1      | 2.90                      | 3.00 | 3.10  |  |  |  |  |

|         | -                         | 0.50 | Ι     |  |  |  |  |

| L       | 0.40                      | 0.53 | 0.80  |  |  |  |  |

| У       | У —                       |      | 0.076 |  |  |  |  |

| ð       | 8                         | 3    | 8     |  |  |  |  |

NOTE :

- S NO NTERI FAD INTERI FAD FLASH SHALL EXCEED

- PER SIDE. DOES NOT INCLUDE DAMBAR LOWABLE DAMBAR PROTRUSION S INT TOTAL IN EXCESS OF THE S ION ROTRUSION ÂLŌ ATE NL COP DIT OF OT BE LOCATED ON THE LO VER RADIUS OR THE FOOT. N MUM SPACE RETWEEN PROTRUSION FOOT. MANUAU SPACE BEINGEN PROTRUSION AND ADJACENT LEAD TO BE 0.0028<sup>+</sup>[0.07mm] TOLERANCE: ±0.010<sup>+</sup>[0.25mm] UNLESS OTHERWISE SPECIFIED. OTHERWISE DIMENSION FOLLOW ACCEPTABLE SPEC

- SPEC. 7. REFERENCE DOCUMENT : JEDEC SPEC MO-187